Questneers : 염한웅 교수 (포항공대 물리학과), 최성율 교수 (카이스트 전기및전자공학부)

실리콘 기반의 CMOS 트랜지스터 소자를 중심으로 형성된 반도체 산업은 AI가 요구하는 대규모 연산을 저전력으로 빠르게 처리하지 못한다는 한계를 보이고 있다. 그러나 트랜지스터의 크기를 줄이는 것만으로는 문제 해결이 본질적으로 불가능하다. 이제 실리콘 기반 소자의 한계가 도래할 때를 대비하여 새로운 소자로 패러다임 전환을 고민해야 한다. 이를 위한 대안적 해법이 무엇이며, 이를 실현시키기 위해 풀어야할 과제는 무엇인가?

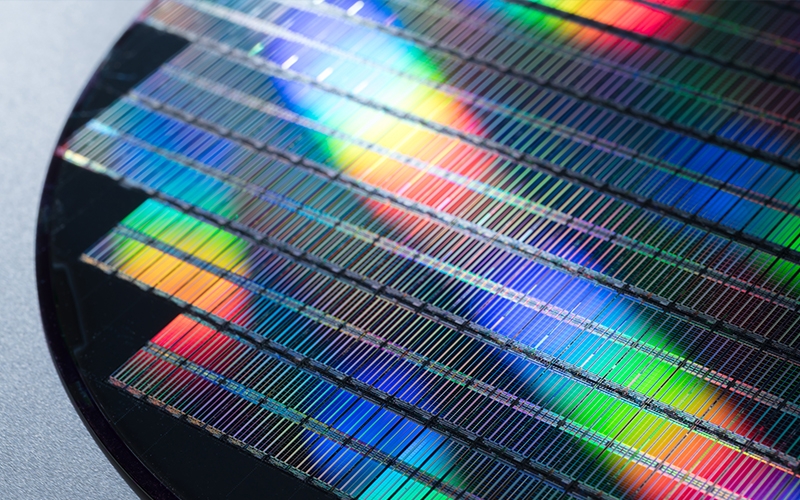

현재 반도체 산업에서 사용하는 소자는 실리콘 기반의 상보적 금속 산화물 반도체(CMOS) 기술을 이용한 트랜지스터이다. 이러한 CMOS 구조를 대면적으로 만들 수 있는 물질은 현재까지 실리콘이 유일하다. 그동안 실리콘 기반 패러다임 하에서 무어의 법칙을 따라 18개월 마다 집적회로의 트랜지스터 수를 2배씩 증가시키면서 빠르게 발전해왔다. 최근에는 칩 하나에 수 백억개의 트랜지스터를 집적할 수 있는 기술수준에 이르렀다. 이러한 기술발전은 트랜지스터를 보다 작게 만드는 것, 즉 다운사이징을 통해 이루어져왔다. 2000년대 초까지만 하더라도 100nm 정도의 트랜지스터의 선폭(node)을 가지고 있었지만, High-K 메탈 게이트(metal gate) 공법을 도입하면서 45nm 공정이 가능해졌고, Fin Field-Effect 트랜지스터 구조를 도입하면서 22nm 이하의 공정이 가능해졌다. 현재 삼성전자와 TSMC에서는 3nm 이하의 기술까지 개발한 상황이다. 하지만 트랜지스터의 다운사이징은 머지않아 한계에 다다를 전망이다. 노드(node)가 작아질수록 누설전류의 문제가 심각해지고 있으며, 무엇보다 상온에서 단위 비트(0/1)를 구분할 수 있는 물리학적인 한계 크기가 1.5nm로 주어져 있기 때문이다. 인공지능의 발전에 따라 요구되는 연산량이 급증하고 있고 저전력으로 동작하는 에너지 효율적인 소자가 요구되는 상황에서, 더 이상 트랜지스터의 다운사이징 만으로는 근본적인 문제 해결방법이 되지 못하는 것이다. 이를 극복하기 위해 현재 시도되는 방향들은 다음과 같다.

첫째, 실리콘 기반의 CMOS-FET의 한계를 보완하기 위한 새로운 소자 기술로서 NC-FET, 터널링-FET 등의 시도가 이루어지고 있다. 이러한 기술들이 3nm 이하의 소자를 구현하는데 중요한 역할을 하겠지만, 이들 역시 근본적으로는 실리콘 기반의 전계효과 트랜지스터의 한계를 공유한다는 단점이 존재한다. 둘째, 극소형 실리콘 트랜지스터의 단점을 극복하기위해 전이금속디칼코게나이드(TMD)와 같은 2차원 반도체 물질을 활용하려는 연구가 많이 진행되고 있다. 2차원 반도체의 경우 결정층의 한 층 크기까지 안정적으로 채널을 줄일 수 있고 단채널효과(short channel effect)를 회피하여, 1nm급 소자기술에 유리하다. 그러나 2차원 반도체 물질을 사용하더라도 CMOS 기술의 과도한 에너지 소모문제와 물리학적인 선폭의 한계는 여전히 동일하게 남는다.

이러한 기술들을 바탕으로 컴퓨팅 효율을 높이기 위해서 다양한 엑셀러레이팅 기술과 패키징 기술이 개발되고 적용될 것이다. 하지만 이러한 CMOS 기반 소자기술은 1.5nm라는 근본적인 물리적 한계에 직면할 수 밖에 없다. 따라서 이 한계를 돌파하기 위해서 기존의 패러다임을 벗어난 완전히 새로운 소자기술로서 폰 노이만 구조를 극복한 새로운 소자기술(non von Neumann architecture)을 고민해야 한다. 이러한 대안적 소자기술들은 에너지소모가 획기적으로 적어야 하며 초고성능 연산을 수행할 수 있어야 하는 조건을 만족해야 한다. 또한 가장 중요하게는 이러한 새로운 컴퓨팅 아키텍쳐를 구현할 소자기술이 기존의 축적된 반도체산업의 플랫폼 위에 큰 무리가 없이 이식될 수 있어야 한다.

실리콘을 벗어난 새로운 소자기술로서 고려할 수 있는 대안들은 다음과 같은 것들이 있을 수 있다. 우선, CMOS 기술을 벗어나 저전력으로 많은 데이터의 연산을 가능하게 하는 멤리스터 소자(memristor)가 있다. 멤리스터는 금속-절연체-금속이 접합되어 있는 구조를 가지며, 트랜지스터와 달리 3단자가 아닌 2단자 소자로 작동하고, 다층 정보처리를 할 수 있는 장점이 있다. 고집적에 유리하고 저전력으로 구동하기 때문에 인공지능 연산에 적합한 뉴로모픽 컴퓨팅(neuromorphic computing)에 도입하기 위해 많은 연구들이 진행되고 있다. 하지만 아직까지는 다중 정보처리를 안정적으로 구현할 수 있는 높은 재현성과 신뢰도를 가지고 다층적인 저항 값들을 구현하는 소자가 만들어지고 있지 않다. 두 번째는 좀 더 미래적인 기술의 가능성으로, 초전도쌍이나 엑시톤과 같이 두 개의 전자들이 결합하여 저항없이 전도되는 상태를 이용하는 기술을 고려할 수 있지만, 아직까지 구체적인 계산을 수행할 수 있는 소자로서는 발전하고 있지 못하다. 세 번째로는 위상절연체로서 저항없이 전도가 가능한 위상전도 채널이 존재하는 물질들을 이용하는 기술이 있을 수 있다. 이 대안의 경우에도 향후 다층 정보처리가 가능한 소자로서 활용하는 기술이 추가적으로 개발되어야 한다. 네 번째는 역시 위상학적으로 보호되어 저항없이 전도되는 솔리톤 입자를 이용하는 기술로서 최근 실리콘과 2D 물질 등에서 구현할 수 있다는 점이 실증된 바 있다. 솔리톤 소자는 저항 발열에 의한 에너지소모가 없을 뿐만 아니라 다진법 연산이 가능하기 때문에 초저전력, 초고성능 소자로서의 가능성이 충분하다.

위에서 논의한 바와 같이 현재의 실리콘 소자기술은 3nm급 소자기술을 계속 다운사이징하면서 발전할 것이고, 결국에는 1.5 nm라는 물리적인 한계사이즈에 도달할 것이다. 이를 위해서 단중기적으로는 TMD와 같은 2D 물질을 통해 부분적인 소재개량을 하면서 현재의 발전추세를 연장해갈 것이다. 그러나 1.5nm의 물리적 한계에 도달한 이후에는 초저전력, 초고성능 컴퓨팅을 구현하기 위해 폰 노인만 컴퓨팅을 넘어서는 컴퓨팅 아키텍쳐와 이를 지원할 FET 이후의 소자기술이 반드시 요구된다. 뉴로모픽 컴퓨팅과 같은 새로운 컴퓨팅을 지원할 소자기술은 다진법 연산과 같은 다중정보처리를 매우 적은 전력소모로 구현해야 하는데, 이를 위해 멤리스터, 엑시톤 소자, 솔리톤 소자 등의 도전과제로서 등장하고 있다. 그러나 아직까지 넘어야 할 기술적 난제가 많고, 특히 기존 실리콘기반 반도체 플랫폼에 조화롭게 통합될 수 있는 방안이 제시되고 있지 않은 실정이다. 이것이 우리가 당면한 반도체 소자기술의 그랜드 퀘스트이다.